# M-993 Region 1 MF Tone Generator

- Generates standard CCITT R1 MF tones

- Digital input control

- Linear (analog) output

- Power output capable of driving standard line

- 14-pin DIP

- Single 5-Volt supply

- Inexpensive 3.58 MHz time base

- Applications include: telephone systems, test equipment

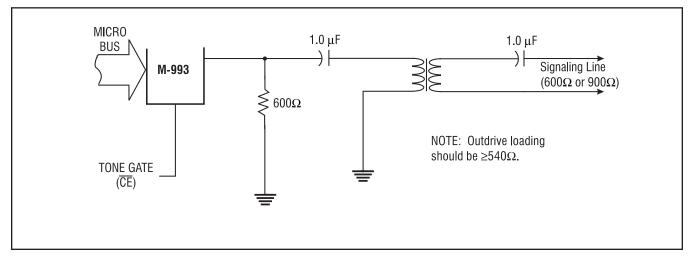

The Teltone M-993 is a monolithic CMOS integrated circuit designed to generate multifrequency (MF) tone pairs for use in trunk signaling. The tones generated conform to CCITT R1 signal recommendations and to AT&T MF standards. The M-993 permits design engineers to implement a highly accurate MF sender with a minimum of space, power, and added components. The accuracy of the tone frequencies is assured through use of an easily obtained 3.58 MHz color burst crystal or an external 3.58 MHz clock source.

# **R1 MF Tone Generation**

MF tones are used to signal between telephone offices and between telephone company central switching equipment and customer equipment.

The M-993 is a highly linear tone generator that produces the tone pairs required for R1 MF signaling. Duration and frequency

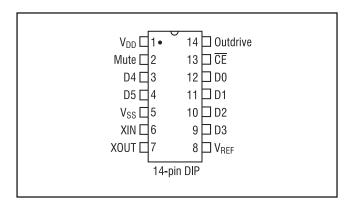

Figure 1 Pin Diagram

selection are digitally controlled (see Table 2 for data settings for a particular tone pair output).

A typical control sequence for the M-993 is: (1) set data lines to desired frequency selection, (2) wait for data lines to settle, (3) drive the chip enable ( $\overline{CE}$ ) low, (4) maintain  $\overline{CE}$  low for desired tone duration (Note: data lines may be changed after data hold time), and (5) return  $\overline{CE}$  to a logic high.

In a bus-oriented system, noise on the data lines may propagate through the device and appear at the output. To safeguard against this, use an external latch to clock the data into the device. In addition, it is good practice to bypass the  $V_{REF}$  pin to ground with a small capacitor (~0.01µF) to reduce power supply

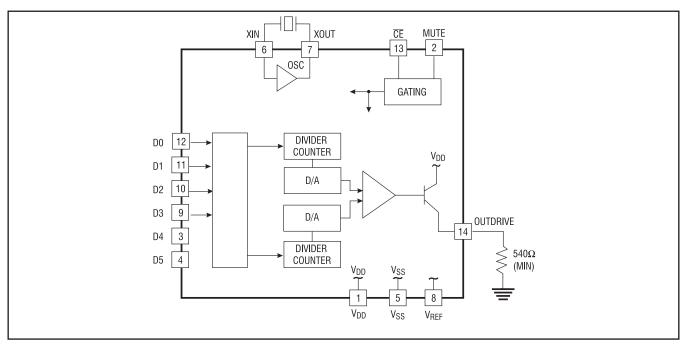

Figure 2 Block Diagram

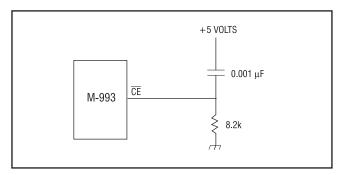

noise. The designer should be aware of device timing requirements and design accordingly. Beware of hardwiring the data input pins for dedicated tone generation. An RC network like that shown in Figure 3 should be used to momentarily reset the device immediately following a power-up to ensure reliable operation.

#### Table 1 Pin Functions

| Pin             | Function                                                       |

|-----------------|----------------------------------------------------------------|

| CE              | Latches data and enables output (active low in-<br>put).       |

| D0 - D3         | Data input pins. (See Table 2.)                                |

| D4-D5           | Leave open.                                                    |

| MUTE            | Output indicates that a signal is being generated at OUTDRIVE. |

| OUTDRIVE        | Linear buffered tone output.                                   |

| V <sub>DD</sub> | Most positive power supply input pin.                          |

| VREF            | Internally generated mid-power supply voltage (output).        |

| V <sub>SS</sub> | Most negative power supply input pin.                          |

| XIN             | Crystal oscillator or digital clock input.                     |

| XOUT            | Crystal oscillator output.                                     |

Figure 3 Power-On Reset Circuit

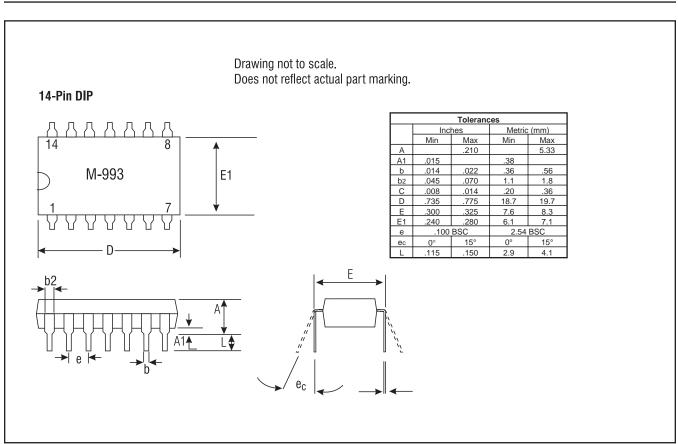

M-993

14-pin plastic DIP

Table 2 Data/Tone Selection

| D3 | D2 | D1 | D0 | Frequency (Hz) Use |      |                |  |

|----|----|----|----|--------------------|------|----------------|--|

|    |    |    |    | 1                  | 2    |                |  |

| 0  | 0  | 0  | 0  | 1100               | 1700 | Key Pulse (KP) |  |

| 0  | 0  | 0  | 1  | 700                | 900  | Digit 1        |  |

| 0  | 0  | 1  | 0  | 700                | 1100 | Digit 2        |  |

| 0  | 0  | 1  | 1  | 900                | 1100 | Digit 3        |  |

| 0  | 1  | 0  | 0  | 700                | 1300 | Digit 4        |  |

| 0  | 1  | 0  | 1  | 900                | 1300 | Digit 5        |  |

| 0  | 1  | 1  | 0  | 1100               | 1300 | Digit 6        |  |

| 0  | 1  | 1  | 1  | 700                | 1500 | Digit 7        |  |

| 1  | 0  | 0  | 0  | 900                | 1500 | Digit 8        |  |

| 1  | 0  | 0  | 1  | 1100               | 1500 | Digit 9        |  |

| 1  | 0  | 1  | 0  | 1300               | 1500 | Digit 0        |  |

| 1  | 0  | 1  | 1  | 1500               | 1700 | ST             |  |

| 1  | 1  | 0  | 0  | 900                | 1700 | ST1            |  |

| 1  | 1  | 0  | 1  | 1300               | 1700 | ST2            |  |

| 1  | 1  | 1  | 0  | 700                | 1700 | ST3            |  |

#### Table 3 Absolute Maximum Ratings (Note 1)

| Storage Temperature                                          | -55 to 125°C                                    |  |  |  |  |

|--------------------------------------------------------------|-------------------------------------------------|--|--|--|--|

| Operating Ambient Temperature                                | -25 to 70°C                                     |  |  |  |  |

| V <sub>DD</sub>                                              | 7.0V                                            |  |  |  |  |

| Any Input Voltage                                            | V <sub>SS</sub> - 0.6 to V <sub>DD</sub> + 0.6V |  |  |  |  |

| Note                                                         |                                                 |  |  |  |  |

| 1. Exceeding these ratings may permanently damage the M-993. |                                                 |  |  |  |  |

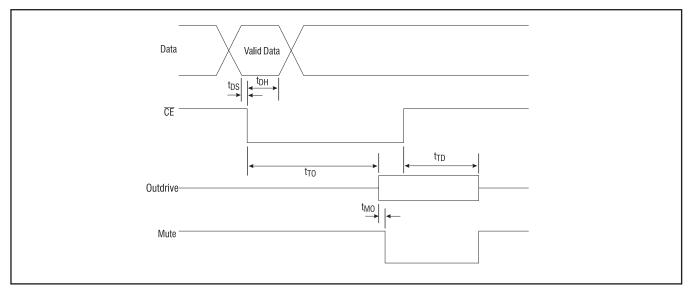

## Figure 4 Timing Diagram

|                                                                                                                                       | Parameter                                                                      | Min                          | Тур          | Max                           | Units | Notes |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------|--------------|-------------------------------|-------|-------|--|--|--|

| Power Supply                                                                                                                          | V <sub>DD</sub>                                                                | 4.75                         | _            | 5.25                          | V     | 1     |  |  |  |

| and Reference                                                                                                                         | Current Drain, I <sub>DD</sub>                                                 | —                            | 2.0/4.0      |                               | mA    | 8     |  |  |  |

|                                                                                                                                       | V <sub>REF</sub> PIN:                                                          |                              |              |                               |       |       |  |  |  |

|                                                                                                                                       | Voltage                                                                        | 48% of V <sub>DD</sub>       | _            | 52% of V <sub>DD</sub>        | %     |       |  |  |  |

|                                                                                                                                       | Internal Resistance from V <sub>REF</sub> to V <sub>DD</sub> , V <sub>SS</sub> | 3.25                         | _            | 6.75                          | kΩ    |       |  |  |  |

| Oscillator                                                                                                                            | Frequency Deviation                                                            | -0.01                        | _            | +0.01                         | %     | 7     |  |  |  |

|                                                                                                                                       | External CLock: (X <sub>OUT</sub> open)                                        |                              |              |                               |       |       |  |  |  |

|                                                                                                                                       | VIL                                                                            | 0                            | _            | 0.2                           | V     |       |  |  |  |

|                                                                                                                                       | VIH                                                                            | V <sub>DD</sub> - 0.2        | _            | V <sub>DD</sub>               | V     |       |  |  |  |

|                                                                                                                                       | Duty Cycle                                                                     | 40                           | _            | 60                            | %     |       |  |  |  |

|                                                                                                                                       | X <sub>IN</sub> , X <sub>OUT</sub> Loading:                                    |                              |              |                               |       |       |  |  |  |

|                                                                                                                                       | Capacitance                                                                    | — [                          | _            | 10                            | pF    | 9     |  |  |  |

|                                                                                                                                       | Resistance                                                                     | 20                           | _            |                               | MΩ    |       |  |  |  |

| Tone Output                                                                                                                           | Frequency Deviation                                                            | -1.5                         | _            | 1.5                           | %     |       |  |  |  |

|                                                                                                                                       | Level                                                                          | 110                          | _            | 180                           | mV    | 2     |  |  |  |

|                                                                                                                                       | Distorting Components                                                          | -35                          | _            |                               | dB    | 2, 3  |  |  |  |

|                                                                                                                                       | Idle                                                                           |                              | _            | -60                           | dBm   | 4     |  |  |  |

|                                                                                                                                       | OUTDRIVE Envelope Rise Time                                                    | —                            | _            | 4                             | ms    | 5     |  |  |  |

| Control                                                                                                                               | DX, CE Pins:                                                                   |                              |              |                               |       |       |  |  |  |

|                                                                                                                                       | VIL                                                                            | —                            | —            | 0.5                           | V     | 6     |  |  |  |

|                                                                                                                                       | VIH                                                                            | 2.5                          | _            |                               | V     |       |  |  |  |

|                                                                                                                                       | Mute Pins:                                                                     |                              |              |                               |       |       |  |  |  |

|                                                                                                                                       | VOL (ISINK = -100 μA)                                                          | —                            | _            | 1.5                           | V     |       |  |  |  |

|                                                                                                                                       | VOH (ISOURCE = 100 μA)                                                         | V <sub>DD</sub> - 1.5        | _            | _                             | V     |       |  |  |  |

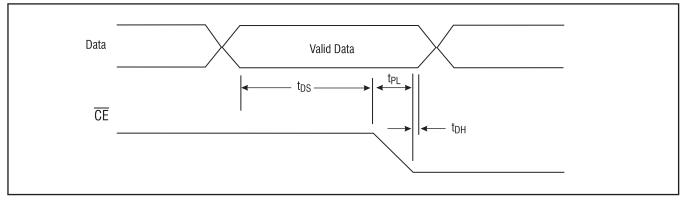

| Timing                                                                                                                                | Data Setup (t <sub>DS</sub> )                                                  | 200                          | _            |                               | ns    | 10    |  |  |  |

|                                                                                                                                       | Data Hold (t <sub>DH</sub> )                                                   | 10                           | _            |                               | ns    | 1     |  |  |  |

|                                                                                                                                       | Chip Enable Fall (t <sub>PL</sub> )                                            |                              | _            | 90                            | ns    | ]     |  |  |  |

|                                                                                                                                       | Tone On Delay (t <sub>TO</sub> )                                               | 5                            | _            |                               | ms    | ]     |  |  |  |

|                                                                                                                                       | Tone Off Delay (t <sub>TD</sub> )                                              | 5                            | _            |                               | ms    |       |  |  |  |

|                                                                                                                                       | Mute Delay from Outdrive (t <sub>MO</sub> )                                    |                              | _            | 200                           | ns    |       |  |  |  |

| Unless otherwise noted, $V_{DD} - V_{SS} = 5 V_{DC}$ , Ta - 25° C<br><b>Notes:</b><br>1. All DC voltages are referenced to $V_{SS}$ . |                                                                                | 5. To 90% n<br>6. For all su | pply voltage | plitude.<br>s in the operatin |       |       |  |  |  |

#### Table 4 Specification

All DC voltages are referenced to V<sub>SS</sub>.

2. Vrms per tone,  $540\Omega$  load.

3. Any one frequency relative to the lowest level output tone

(f<4000 Hz).

4. 0 dBm = 0.775 Vrms.

7. At XOUT pin as compared to 3.579545 MHz.

8. OUTDRIVE with load >5 K $\Omega$ /OUTDRIVE with 540 $\Omega$  load.

9. Crystal oscillator active.

10. Measured 90% to 10%.

# Figure 5 Expanded Timing Diagram

Figure 6 Package Dimensions

## **Figure 7 Typical Application**